# Intel<sup>®</sup> Simics<sup>®</sup> Virtual Platforms in Industry

Dr. Jakob Engblom, Director, Simulation Technology Ecosystem

Intel, Stockholm, Sweden

jakob.engblom@intel.com

### **About Me: Jakob Engblom**

### Currently:

Swede

Director (of Simulation Technology Ecosystem), Simics Core team, at Intel in Stockholm,

### Education:

MSc, Computer Science, and PhD, Real-Time Systems, Uppsala

### Experience: virtual platforms, simulation, embedded systems

- Product management, product marketing, technical sales, technical marketing, business development, training development, demos, ... At IAR Systems, Virtutech, Wind River, and Intel

- My own blog, since 2007:

- https://jakob.engbloms.se

### Intel software blog:

<u>https://community.intel.com/t5/Blogs/Products-and-Solutions/Software/bg-p/blog-software</u>

# Introducing Intel®

### **Product Leadership**

### **Open Platforms**

**700+** Foundations and standards bodies with Intel 4.50+ Software tools & resources

on the Intel Developer Catalog for developers to create and deploy solutions **150+** Software tools & resources on the Intel Developers

Catalog for Al workloads

Intel software powers much of the world's computing

Linux kernel corporate contributor since 2007

top 10

contributor to Kubernetes

intel. ONE INTEL OVERVIEW

### **Geographically Diverse Manufacturing Capacity**

📕 Wafer Fabs 🗧 Assembly & Test 📕 Future Site

intel. ONE INTEL OVERVIEW

### The Intel<sup>®</sup> Simics<sup>®</sup> Simulator

# The History of the Intel® Simics® Simulator

### Development started in 1991

- Spin-off from research project

- Pre-silicon OS bring-up.

- Virtutech founded in 1998

- Sun\* & Ericsson\* first customers

Acquired by Intel in 2010

Wide usage

- Intel-internal

- Intel ecosystem

- Commercial customers via Wind River\*

- Academics and OSS via public release

### Major milestones

- 2.0: Heterogeneous system models

- 3.0: Reverse execution & debug, 2005

- 3.2: Intel virtualization acceleration

- 4.0: Multi-threaded (coarse), 2008

- 4.2: Distributed simulation, 2009

- 5: Multicore multithreading, 2015

- 6: More threading & better support for model integrations, 2018

- Integration with power, thermal, performance models

- Continuously adding features

- 7: Clean up & modernizations, 2023

- Removing older APIs and features to focus on the new

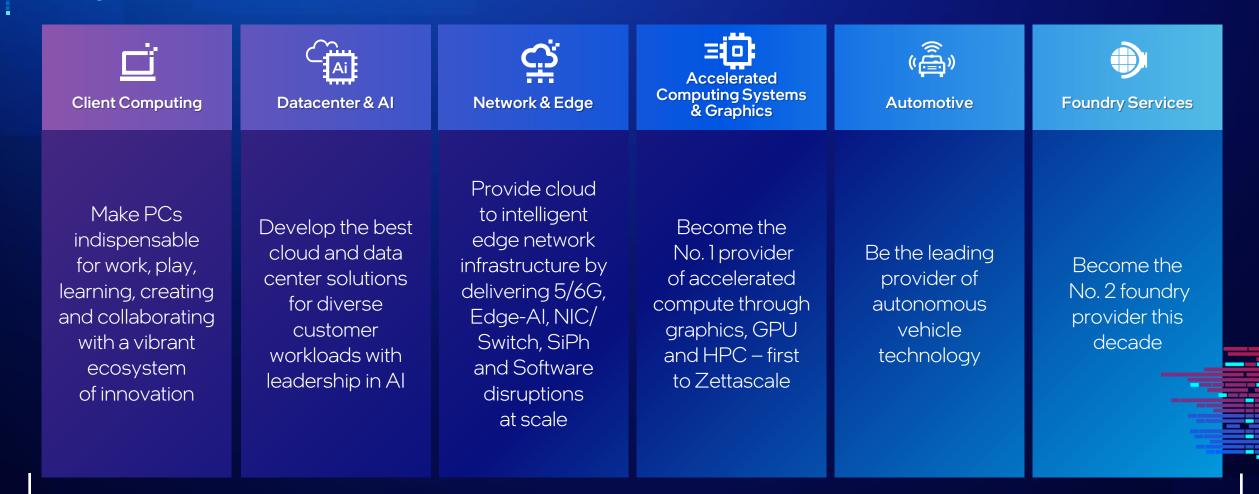

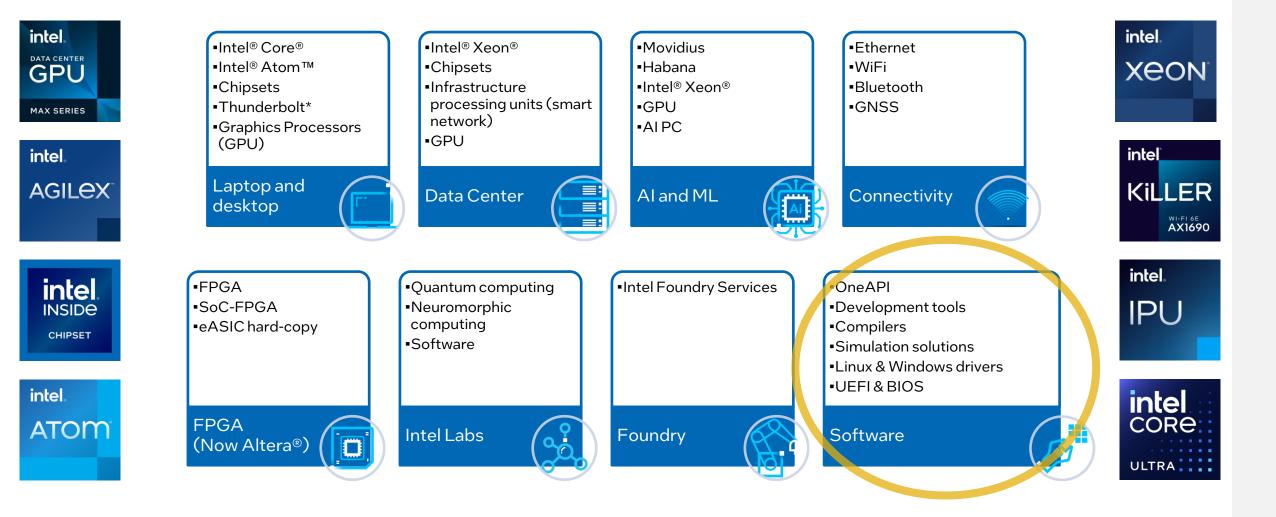

### What Does Intel® Do and Where do We Fit?

11

# Virtual Platforms Why and What?

### Hardware: A Hard Development Platform?

### Hardware is Hard When it is in...

Not yet available

#### Flaky prototype stage

#### Not available anymore

### Hardware is Hard When it is...

Inconveniently large & complex

#### Inaccessible & expensive

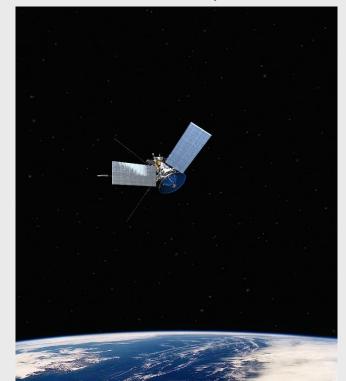

### The Idea of a Virtual Platform

### Run your software without the hardware – on a software model

Copyright © Intel 2024

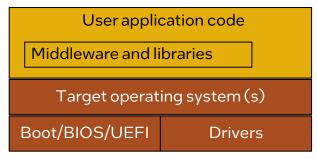

# **Running the Real Software**

### Purpose:

• Test & debug the **software** and the **software-visible** aspects of the hardware

### "Software" can mean many things...

- Firmware, that is deeply hidden inside a chip

- BIOS/Bootloader/UEFI, that is used to boot the machine

- Device drivers, that manage hardware for an operating system

- Operating systems

- Middleware, providing services for other software

- Applications, that any programmer would write

- Distributed systems, software running across many separate machines

- From bytes to terabytes of code!

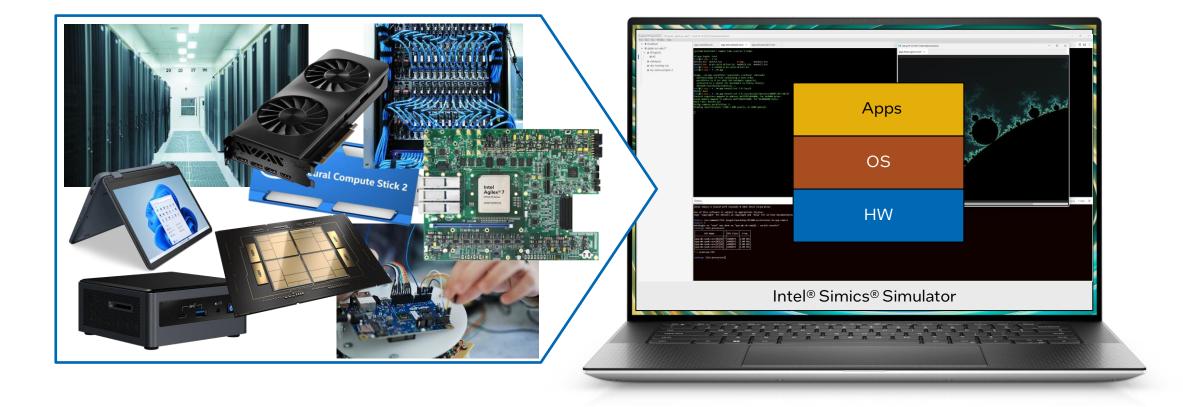

### Inside a Typical Virtual Platform

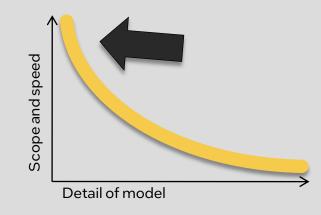

# Intel<sup>®</sup> Simics<sup>®</sup> Simulation: Level of Abstraction

#### Goal: Fast & scalable simulation

#### Goal: run the real software

Target model includes all software-visible functional aspects of hardware, such as processor instructions, supervisor modes, device registers, interrupts, etc. Transaction-level modeling (TLM)

#### Model function & basic timing

| Processor<br>instruction<br>set | System<br>memory map<br>(not bus<br>system) | Device<br>register<br>interface                 |

|---------------------------------|---------------------------------------------|-------------------------------------------------|

| Loose timing<br>model           | Packet-level<br>models of<br>networks       | Event-driven<br>simulation, not<br>cycle-driven |

#### Lazy and agile modeling

Build up the model piece by piece over time, as use cases materialize or become possible. Only model what is needed for current use cases.

#### Add details when and where needed

| Processor<br>performance<br>models |              | Device<br>performance<br>models |    |                                | Cache and<br>memory<br>system<br>models |  |

|------------------------------------|--------------|---------------------------------|----|--------------------------------|-----------------------------------------|--|

|                                    | Hardware RTL |                                 | tł | Power and<br>thermal<br>models |                                         |  |

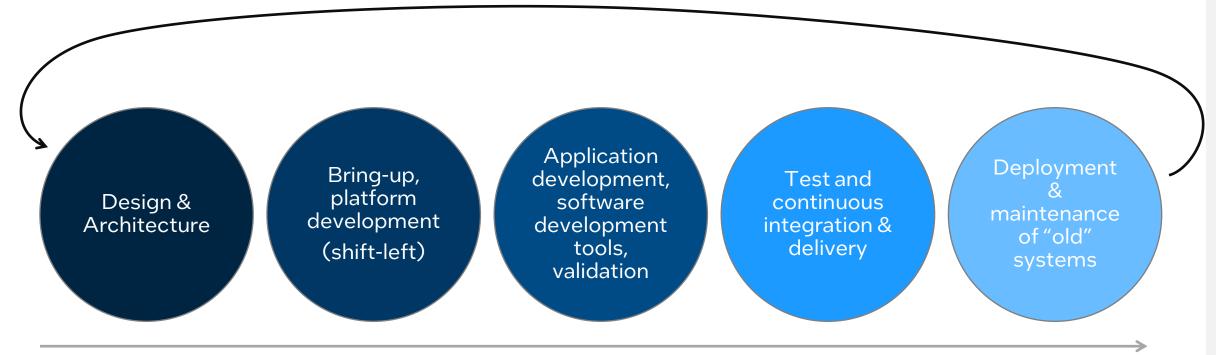

### The Intel<sup>®</sup> Simics<sup>®</sup> Simulator

**Use Cases**

### Virtual Platforms & the Product Lifecycle

### **Product Timeline**

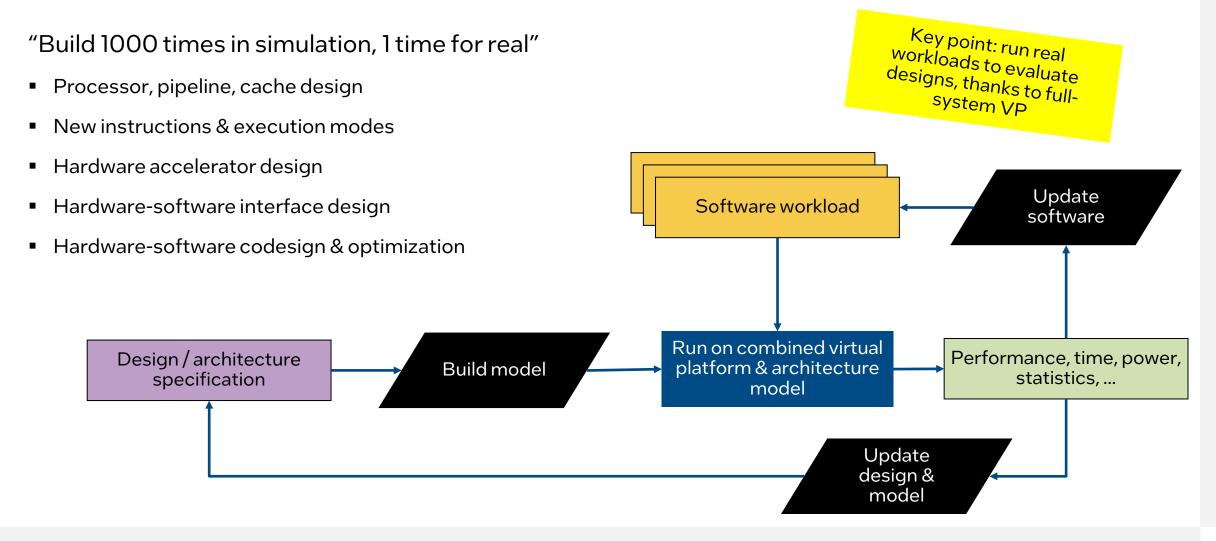

# **Getting the Architecture Right**

# Computer Architecture (on Virtual Platform)

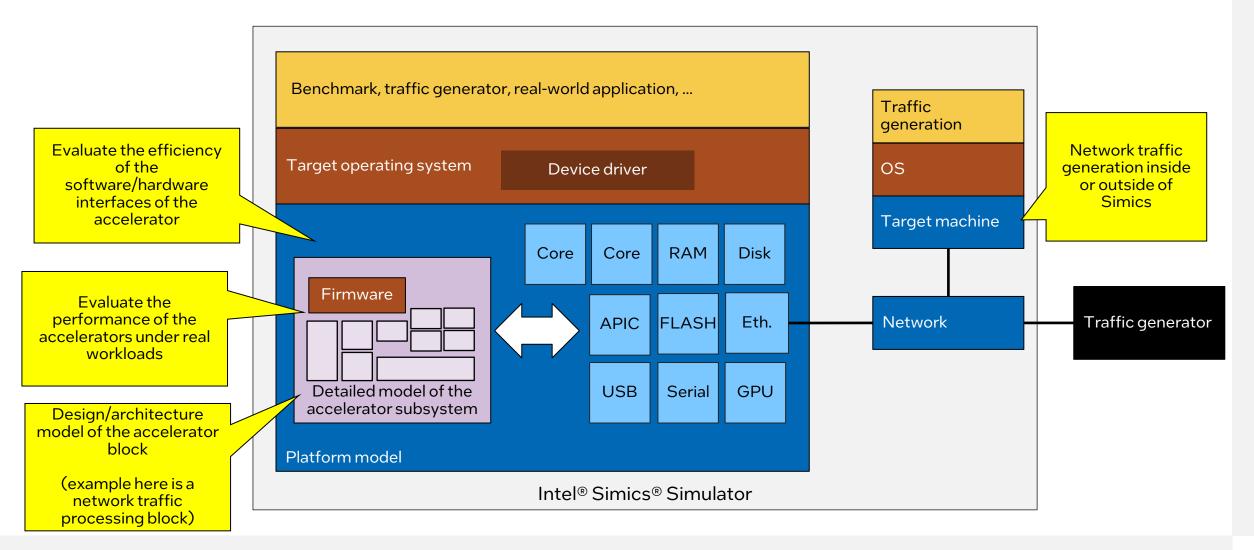

### **Computer Architecture: for Subsystem**

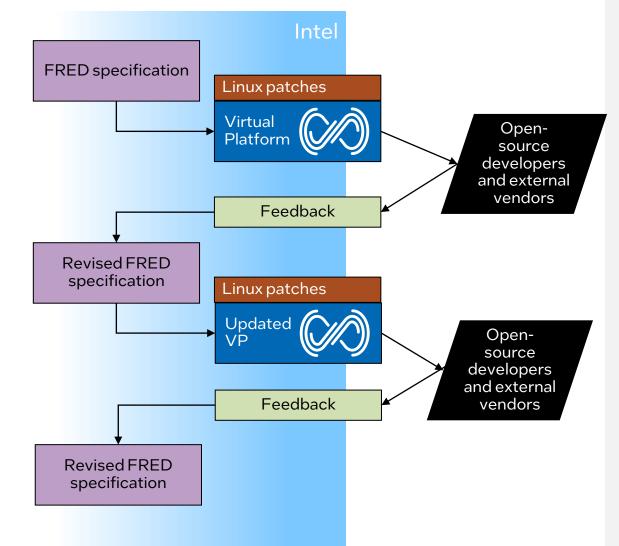

# Instruction-Set-Level Computer Architecture

Architecture happens at the instruction-set level as well as microarchitecture

Example: "Flexible Return and Event Delivery" (FRED)

New way to handle exceptions and interrupts in the Intel Architecture

Intel<sup>®</sup> Simics<sup>®</sup> virtual platforms used as "test hardware" for external software developers

- For Linux developers, provided together with Linux kernel patches from Intel's Linux developers – software is needed

- Collect feedback from external (operatingsystem) developers, improve the design

# **Getting Software Done Early**

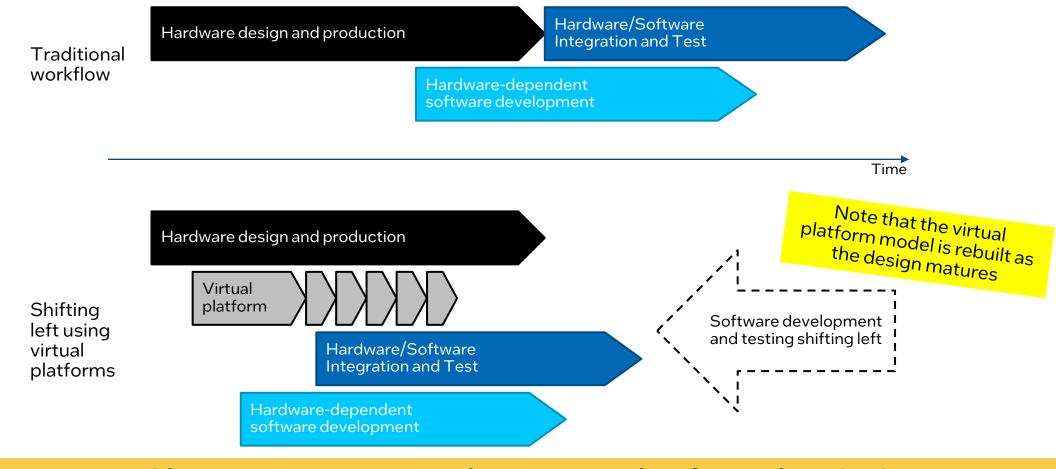

# Shift-Left / Early Software Development

### Classic use case – Earliest examples from the 1950s

### Shift-Left: With the Ecosystem

Board designer adds more components, ports more operating systems, validates additional functionality OEMs build on the boards to build complete products.

Digital twins Virtual system integration

**OEM Product**

Could be the same company as the board designer, or yet another company

Silicon vendor builds basic code, makes sure the platform works

### (Custom) Board

Typically, this is a customer of the silicon vendor, a separate company

Copyright © Intel 2024

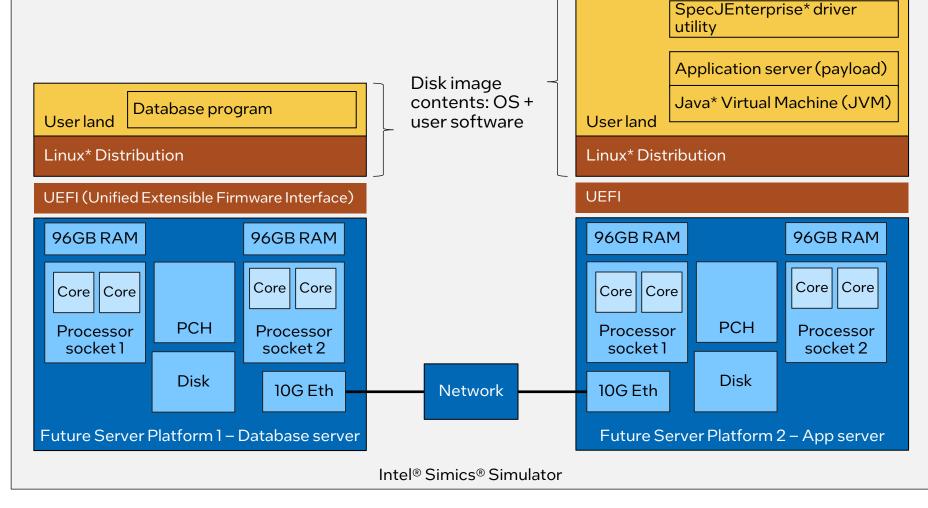

# Testing Software at the System Level

## **System-Scale Simulation Example**

Update software stack to use latest hardware instruction sets and features

Ensure integration of hardware, boot code, drivers, OS, and applications work – before the silicon arrives

*This particular example: silicon vendor + software vendor cooperating on next-gen hardware tuning*

https://software.intel.com/en-us/blogs/2018/03/15/software-on-wind-river-simics-virtual-platforms-then-and-now

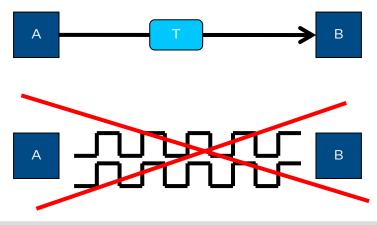

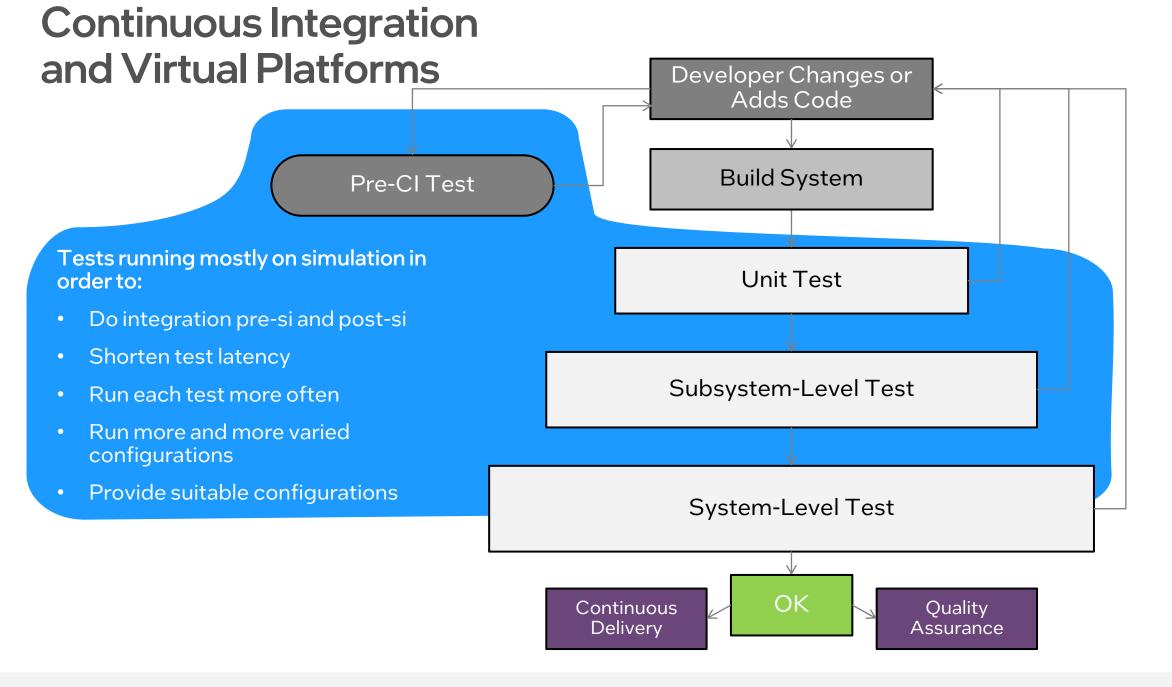

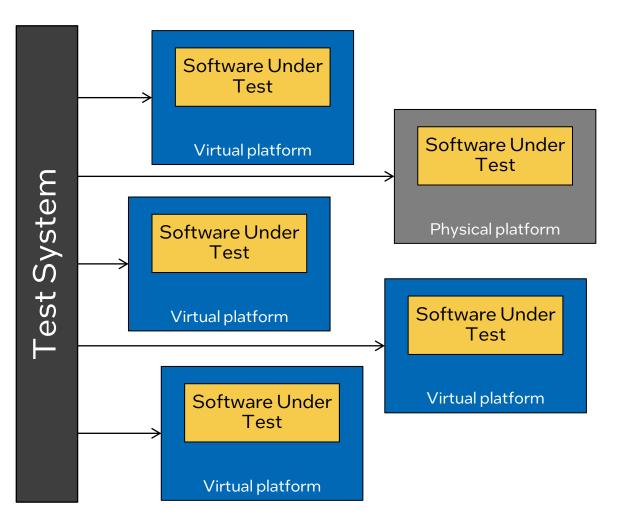

# **Allowing More Tests for Difficult Hardware**

Hardware availability is often a bottleneck in embedded systems testing

Classic customer case

- Hardware = Integration testing every week

- Bugs creep back in

- Impossible to go Agile

- Virtual platforms provided more targets

- Integration testing *daily*

- = Higher quality, less rework, more agile development flow

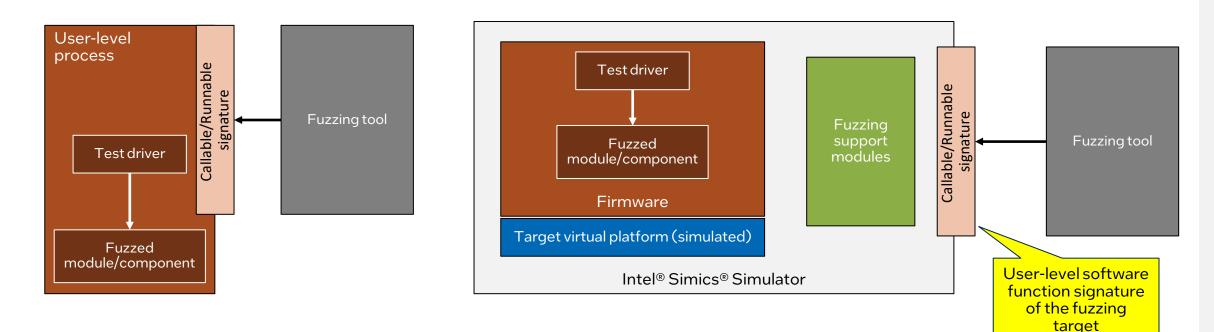

## Virtual-Platform-Based Guided Fuzzing

Concept: Make the virtual platform look like a user-level program

- Reuse existing fuzzers and their fuzzing logic as-is...

- ... while facilitating access to the firmware using virtual-platform techniques

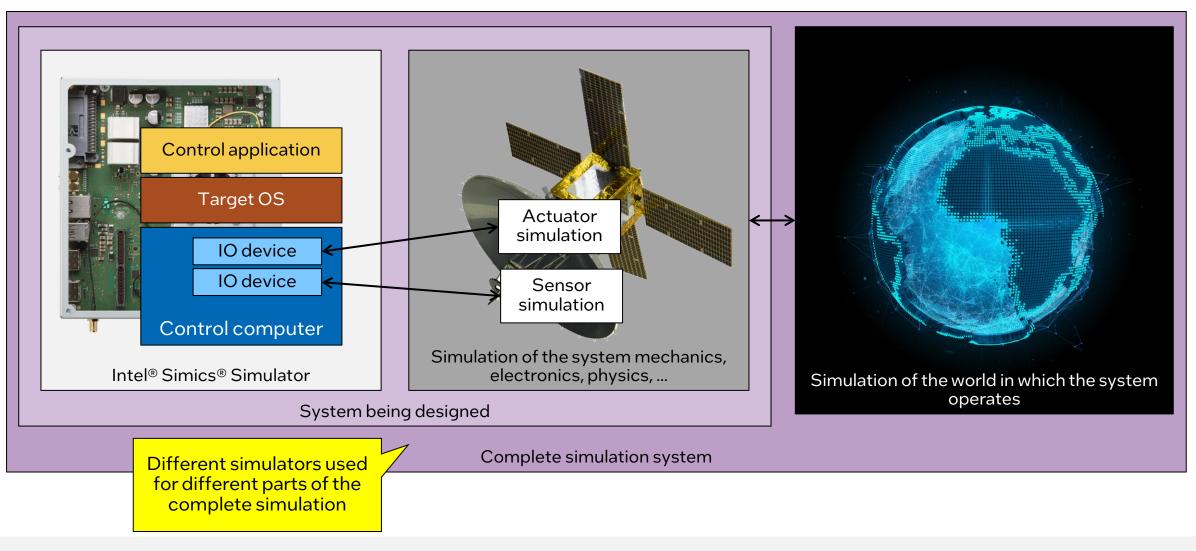

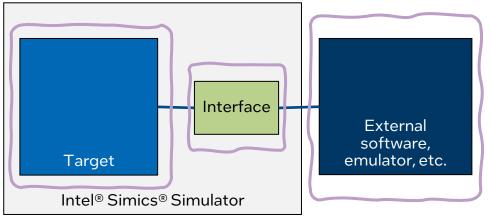

### **Integrating Environment Simulation**

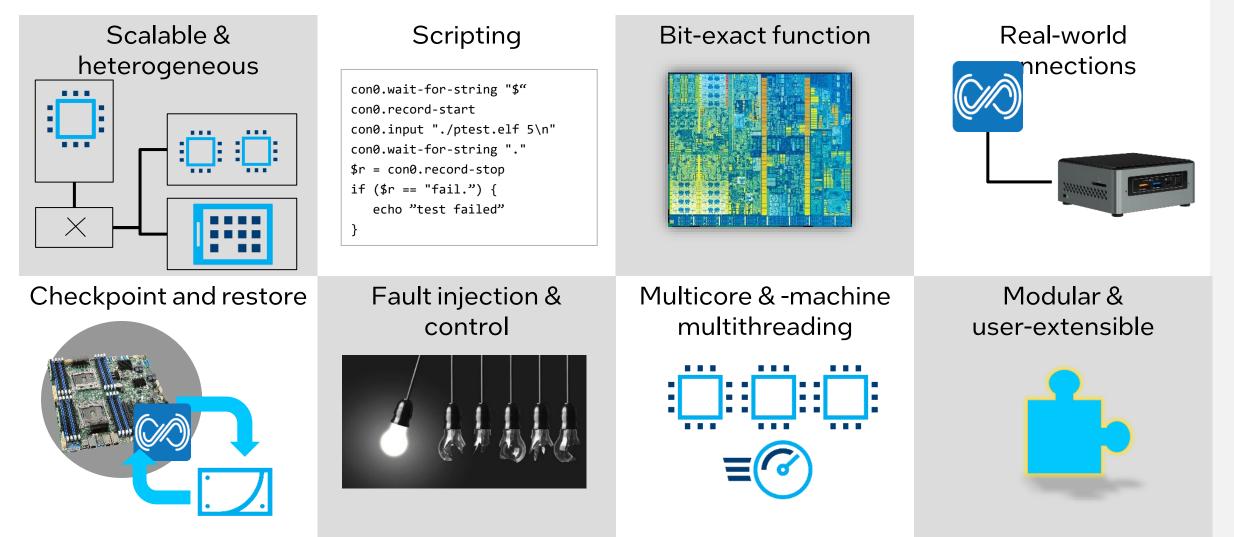

### Intel<sup>®</sup> Simics<sup>®</sup> Simulator Technology

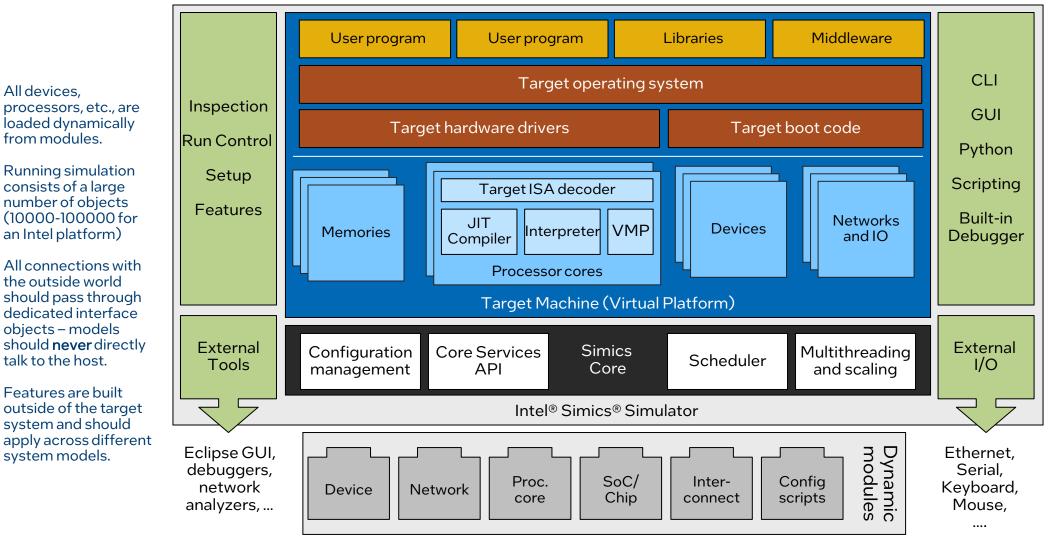

### Intel<sup>®</sup> Simics<sup>®</sup> Simulator Architecture

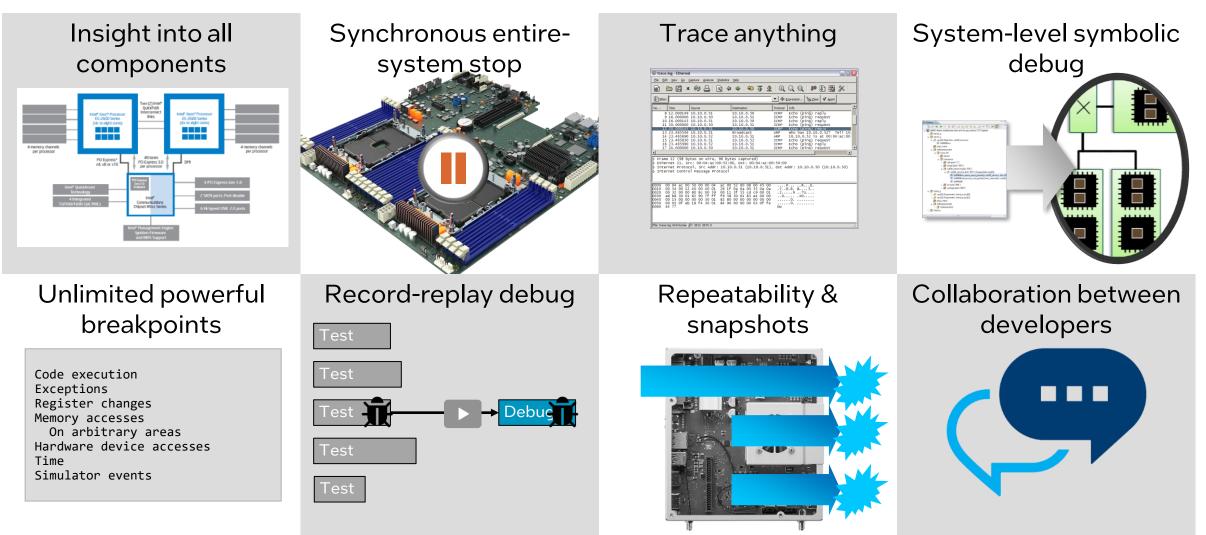

### **System Level Features**

## **Debugging Features**

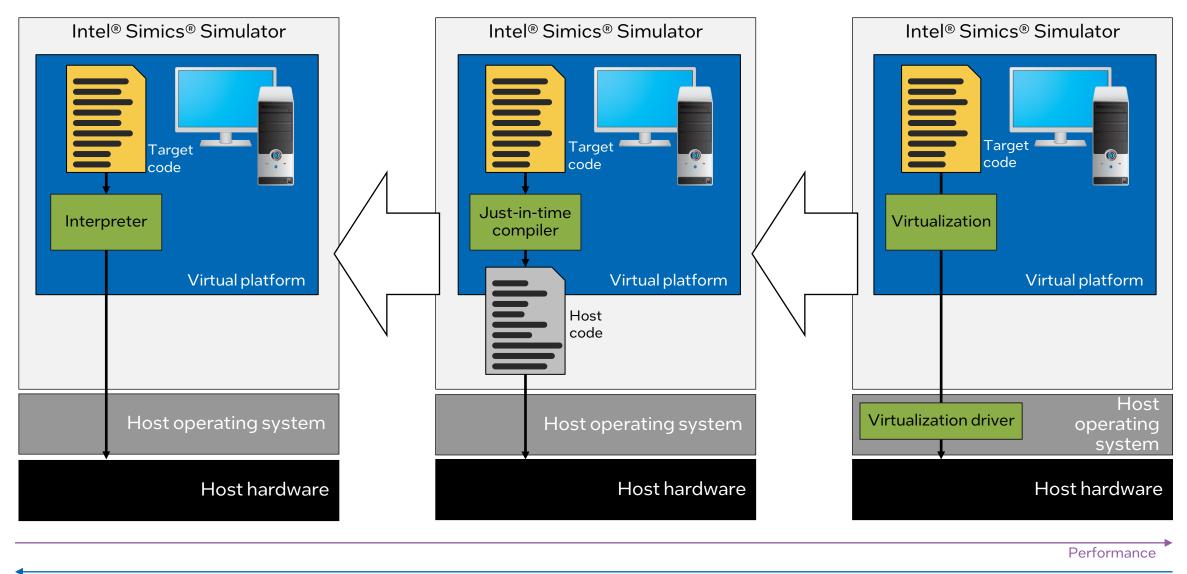

#### How to build a fast virtual platform

#### Fast Instruction-Set Simulator (ISS)

Functional abstraction level Just-in-time compilation (JIT) Virtualization Simplified timing Temporal decoupling

#### **Fast Device Models**

Transaction-Level Modeling (TLM)

**Event-driven simulation**

Simplified timing

#### Efficient Framework

Reduce overheads

Multithreading

Optimize, optimize, optimize

#### **Tailored Configurations**

Configurations optimized for each use case

Highest-possible level of abstraction

Use different models in different cases

#### What Performance do you Need for a Particular Use Case?

| Slowdown | Use cases where this works                                                           | Notes                                                            |

|----------|--------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 1/10     | Long-term testing of a mostly idle system                                            | Depends on system being idle,<br>or very slow in the real world  |

| 1        | Hardware-in-the-loop                                                                 | Simulators trying to stay locked to real-<br>world time          |

| 10       | Edit-compile-test, volume software testing,<br>interactive usage of virtual platform |                                                                  |

| 100      | Automatic testing of complex setups                                                  | Slow execution due to large models or some details in the models |

| 100000   | Computer architecture, detailed performance<br>modeling, run short segments of code  | Design models run at 100k slowdown or<br>more                    |

## Intel® Simics® Simulator Instruction Execution

Completeness

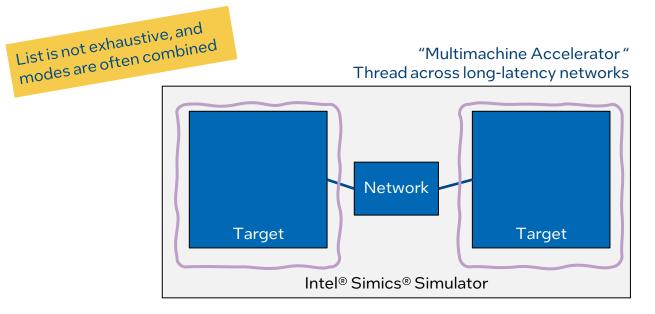

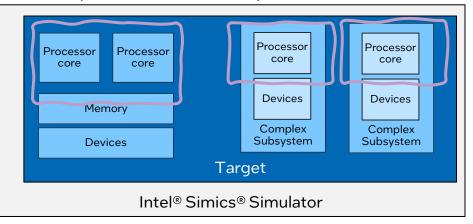

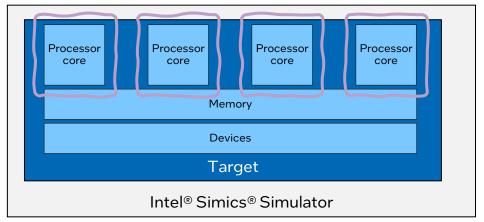

## Threading in the Simics<sup>®</sup> Simulator – Use Cases

"Subsystem multithreading" Run separate (definition) subsystems on their own threads

"Multicore Accelerator" (MCA) Thread between processor cores sharing memory

#### Multithreading as coding pattern Use a thread to interact with the outside asynchronous world

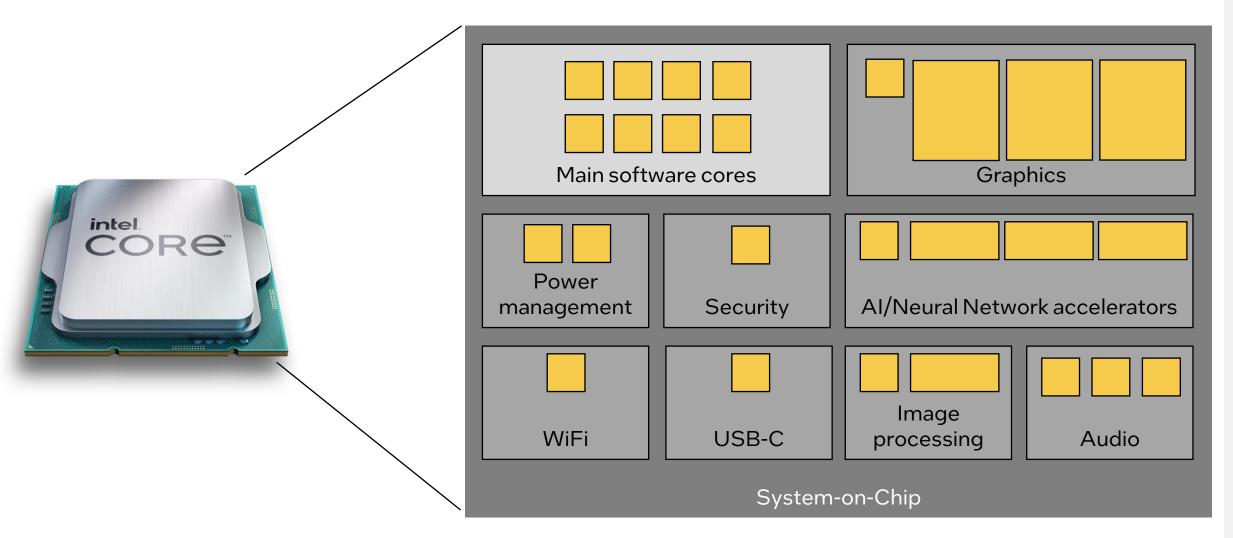

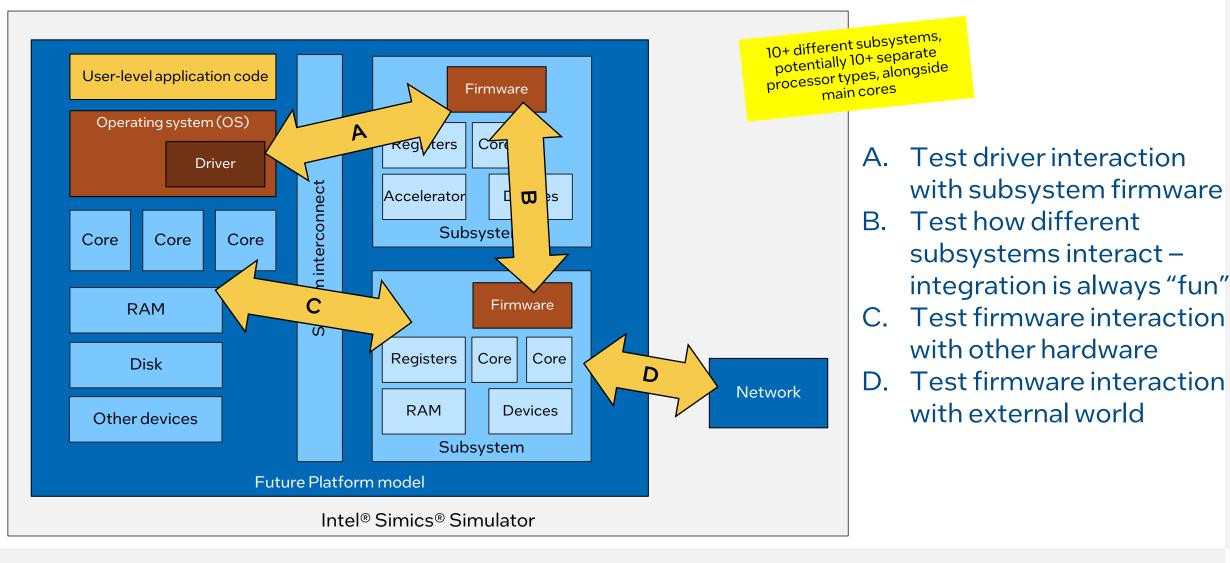

## Inside a Modern System-on-Chip (SoC)

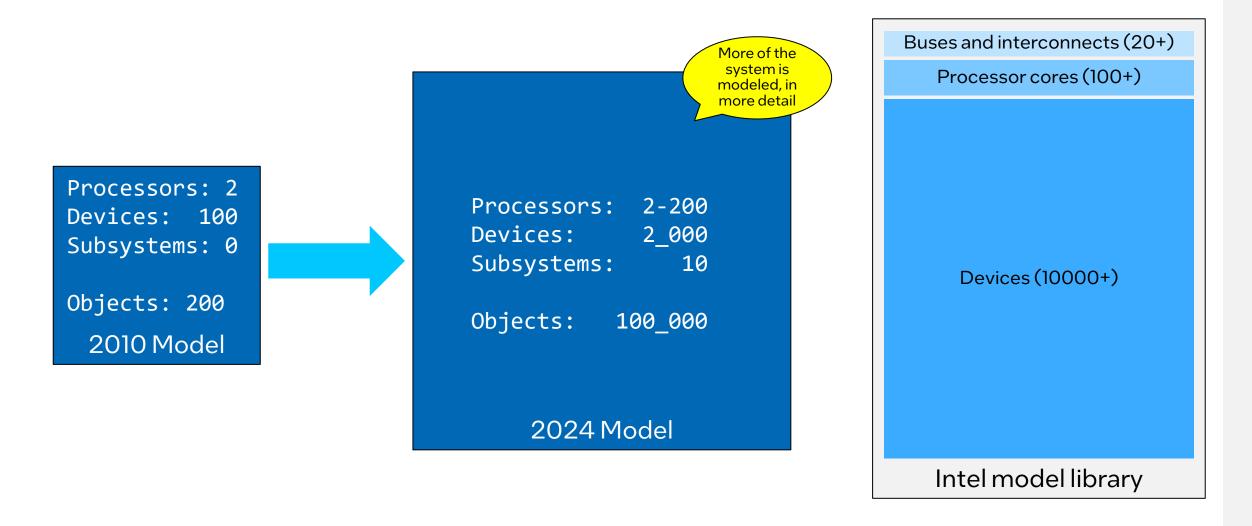

## **Result: Virtual Platforms get Bigger Over Time**

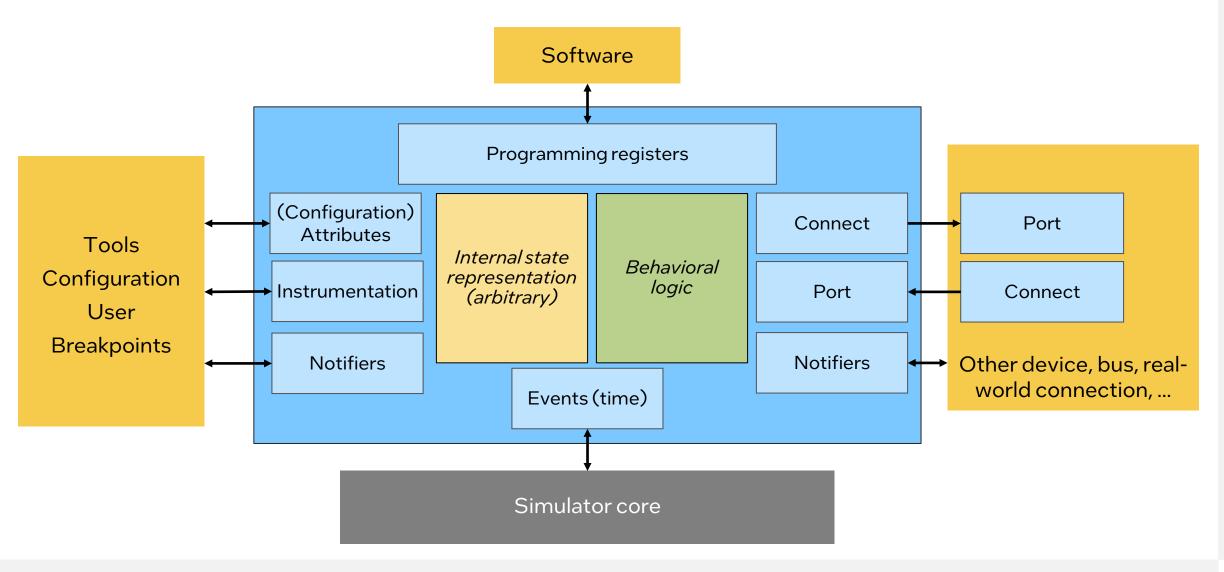

#### Parts of a Device Model – More Details

## The Device Modeling Language;

import "simics/devs/i2c.dml"; // generic i2c import "platform-i2c.dml"; // i2c logic s import "fuse-common.dml"; // common plat

// generic i2c // i2c logic shared with other platforms // common platform fuse mechanisms

#### https://github.com/intel/device-modeling-language

Make device modeling easy

Make it hard to write bad models

Provide natural modeling constructs

- Register, bit field, banks, connects, ...

- Readability and maintainability

- Easy to generate register layouts from machine-readable specifications

#### Powerful templating mechanisms

- Common behaviors

- Common types of devices

- Support library behind code generation

```

• ...

```

Generates C code with Intel® Simics® Simulator API calls

```

// generated code with register declarations

import "DevBank_gen_code.dml";

```

```

// instantiate the register bank from the file

bank regs is i2c_ctrl_reg_bank {

register hst_cnt { // Added manual code

method write_action() {

if (START.get() != 0) {

START.set(0);

send_start();

}

// Start();

// Start();

```

// Generated file DevBank\_gen\_code.dml

dml 1.4;

import "access\_templates\_14.dml";

```

template i2c_ctrl_reg_bank {

param bank_reset_signal default undefined;

```

```

register hst_sts@ 0x00 is (read_write) "Host Status";register hst_cnt@ 0x02 is (read_write) "Host Control";// array of registers@ 0x08 + i is (read_write) "Transmit data";

```

```

// flesh out fields in hst_sts

register hst_sts {

field BYTE_DONE_STS @ [7:7] is (write_1_clears);

field INUSE_STS @ [6:6] is (write_1_clears);

...

```

## Working with Firmware and Subsystems

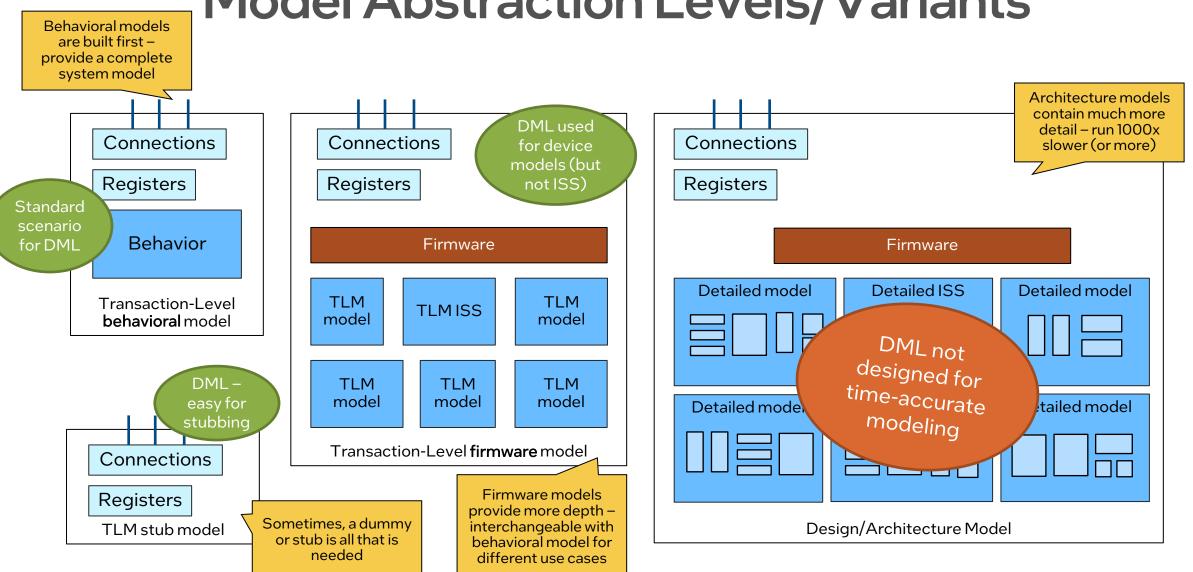

#### Model Abstraction Levels/Variants

## Coding in All the Languages $\odot$

|                     | C/C++ | Python | Device Modeling<br>Language | SystemC | Javascript | Rust | Simgen | Scripts of various<br>types |

|---------------------|-------|--------|-----------------------------|---------|------------|------|--------|-----------------------------|

| Simulator core      | Х     | Х      |                             |         |            |      |        | Х                           |

| User features       | х     | х      |                             |         |            |      |        | х                           |

| User interfaces     |       | х      |                             |         | Х          |      |        | х                           |

| Utilities and tools | Х     | Х      |                             |         | Х          | х    |        | х                           |

| Processor<br>models |       |        |                             |         |            |      | х      | х                           |

| Device models       | Х     | х      | х                           | Х       |            |      |        | х                           |

# Open for questions and discussions!

#### Public Release of Intel® Simics® and Intel® Integrated Simulation Infrastructure with Modeling (Intel® ISIM)

## Download and Learn More at <a href="https://software.intel.com/intel-isim">https://software.intel.com/intel-isim</a>

## Legal Disclaimers

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete <u>http://www.intel.com/performance</u>.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

\*Other names and brands may be claimed as the property of others.